Consumer devices such as mobile audio players, set-top boxes (STBs), digital television (DTV), and digital versatile disc (DVD) players and recorders are typically implemented using a multi-function system-on-chip (SOC). Such SOC mainly performs two functions: application processing and video/audio signal processing. Application processing (or main processing) is usually implemented by a programmable core such as a MIPS processor. Due to the degree of computational complexity, video signal processing is done using dedicated hardware. To some extent, the computational requirements for audio signal processing are not as large as the processing of video signals. In the past, they were processed using fixed line logic or a digital signal processor (DSP).

This article refers to the address: http://

However, as the user's product needs to support more complex algorithms, the demand for the audio subsystem is also increasing, and advanced pre/post processing and full duplex require simultaneous codec. As audio requirements increase, the frequency of processors increases as a result of architectural innovations, enabling programmable processors like MIPS Technologies to implement demanding audio applications with the main functions.

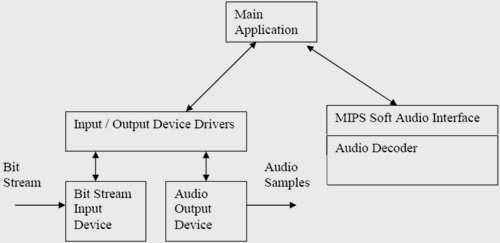

It is possible to build two types of SOC structures for executing audio applications on a MIPS core: (1) one as the main processing CPU, the other as the dedicated CPU for audio processing (see Figure 1), or (2) A single CPU acts as both main processing and audio processing. Using MIPS processors can bring significant benefits to audio processing. The most important is the advantage that this type of solution provides the following features:

高度Single processor architecture for highly integrated SOC solutions

⊙ Reduce the cost of the entire SOC design and manufacturing process

⊙Programmable audio processor extends the life cycle of SOC design

⊙The advantage of fast market launch

⊙MIPS soft audio interface facilitates application development and integration

Multi-core SOC audio architecture

In the case of multiple cores, the main CPU runs the operating system, end-user applications and services, while the audio processing functions are run with a dedicated audio processor. Obtaining several licenses from MIPS Technologies will result in SOC tools for consumer electronics devices specifically for the MIPS audio processing core. In short, a programmable solution is available for processors using MIPS for audio design. Programmability means that an existing design can be easily adapted to a wide variety of audio algorithms. This can provide two important advantages: the ability of a single SOC can be used for multiple end-user applications; while extending the lifecycle of the SOC design to keep pace with the rapid evolution and change of audio standards.

The advantage of a dedicated audio processor is that it does not compete with other applications for CPU cycles, so there is plenty of room for it. The margin of this audio coprocessor can be used in a variety of ways: (1) the alternate CPU cycle can be used to encode and decode multiple streams simultaneously; (2) it can guarantee the highest audio quality in high-end designs; Or (3) the margin can reduce the frequency of the processor by lowering the voltage, thus reducing the power consumption of the audio subsystem and the entire SOC.

The advantages of using a programmable processor to implement an audio algorithm are particularly evident in its configuration because of its flexibility to conform to the evolving global audio standards. With dedicated DSPs, current performance and power requirements may be met, but they may not be able to meet future needs based on changes. MIPS' audio processors provide a clear and easy migration path to high-performance processors and are binary compatible with their predecessors.

Figure 1 audio processing architecture

When the audio processing function of a core is completed separately from the main CPU, a communication mechanism is required between the main CPU and the audio processor. Establishing a communication interface between two MIPS cores is much simpler than between a MIPS CPU and a DSP. For example, the LL and SC (load-connect/store-condition) instructions available on the MIPS CPU can be used to easily establish communication and synchronization mechanisms.

Single core SOC audio architecture

In a single-core environment, the biggest benefit is to perform audio on the MIPS host processor by completely eliminating the DSP or fixed-line audio modules. This reduces both die size and overall system debug time. This, in turn, guarantees cost reductions and faster market launches.

With a real-time operating system (RTOS) running on the main CPU, audio processing can complete one of the threads (tasks) of the system. The RTOS must ensure that this audio thread gets enough timing slots to complete its task in a timely manner. In general, audio processing will only require a small portion of the CPU cycle; therefore, this requirement can be easily met. In addition to the RTOS, this single processor can also perform other applications such as video control. The proper timing mechanism is necessary to ensure that all tasks are completed on time.

In a single-core solution, the performance of the audio application is degraded due to interference from instructions and/or data caches. This degradation is a specific combination of the operating system and other control functions performed on the processor. If performance degradation is unacceptable, you may need to use one of two methods. Once the cause of the degradation is isolated from the instruction or data cache, the first method required is to lock the cache line that controls critical functions or data arrays.

If the cache line lock method is not ideal, then a dedicated scratch pad RAM (SPRAM) can be used. SPRAM is an on-chip memory that provides predictable low latency for MIPS processor execution selection. If necessary, the capacity of the SPRAM may be much larger than the capacity of the cache, however, usually a small amount of SPRAM may help bring significant performance to the application. Errors in the instruction cache in the audio decoder can be reduced by loading the "text" (code) segments of the key functions of the software audio decoder in the SPRAM. Alternate use of SPRAM maintains a common array of data to reduce data cache errors.

The lowest cost total solution: using MIPS processors for audio

When making system architecture decisions, there are several major cost factors to consider, such as: authorization, royalties, die size, development tools, and design time. Especially in low-end systems, if you use a single-core SOC architecture, you can completely eliminate the DSP, reduce the size of the entire die, and do not have to pay the DSP licensing fees and royalties. This will significantly reduce the overall cost of SOC manufacturers and OEMs.

Regardless of whether SOC vendors choose to run audio on a dedicated core or audio on the main CPU, software development tools are less expensive because the same toolchain can be used to develop applications based on the main CPU and audio. A major component of development tool costs is tool-related maintenance. In the case of a dedicated DSP, this can be a large part of the overall cost.

Developers who use a MIPS core to implement control functions and use DSP for audio processing must be familiar with two different development environments. A typical development environment might include an operating system, compiler, simulator, emulator, debugger, stitch tool, probe, and profiler. However, when the same kernel is used again, it is only necessary to be familiar with a development environment, thereby reducing overall design time and design cost.

Pre-optimized audio software offers time-to-market advantages

MIPS Technologies and its audio software partners offer a wide range of optimized audio applications for the MIPS32 core. These applications include a variety of standard audio and multimedia digital signal codecs for consumer products such as digital cameras, digital video cameras, set-top boxes, digital TVs and DVD players. Together with the high-performance development tools provided by MIPS Technologies, these highly optimized algorithms help developers focus on the development and integration of driver applications without the need to optimize algorithms for standard audio.

For those wishing to tune other audio/DSP algorithms, the MIPS DSP Library is available as part of the MIPS Software Toolkit. This library has a wide range of signal processing functions for speech compression, echo cancellation, noise cancellation, channel equalization, audio processing, and general functions such as filters and FFT. These features have been optimized in MESS Technologies' multiple processor families.

The MIPS core has many features that help to effectively implement applications like DSP. Optimized audio codecs and DSP libraries can take advantage of these features to provide important advantages:

æä¾› Provides the best possible audio quality for internal calculations using 32-bit integer data in all audio algorithms.

The MIPS32 Multiply-Accumulate (MADD) instruction is very efficient when encoding DSP MAC operations.

æ•°æ® Data prefetch instructions in the MIPS32 architecture can be used when appropriate in the DSP loop. This allows data prefetch to enter the next iteration of the cache while executing the current iteration of instructions. Significant savings in overall uptime can be achieved by avoiding cached error latency.

The small footprint of the memory is ideal for most of the most cost-effective solutions. The MIPS16 Application Specific Extension (ASE) can be used to reduce program code size. This can be achieved by simply using an edit time selection to significantly reduce the size of the program code.

Figure 2 Application example of MIPS audio decoding

In addition to the above features, the software uses other technologies to get the highest possible performance:

⊙MIPS32 assembly tool has the ability to enhance the manual coding of key computational calculations;

人工 Artificial timing built on the kernel to the core minimizes load usage (after the data required by the instruction begins execution, the load instruction data from the cache/memory system arrives – until the data is available, the processor Bottleneck that won't run)

⊙ Loop unrolling and software pipeline operations are available for optimal code timing.

To provide maximum flexibility, all algorithms of the MIPS consumer audio platform can be implemented in software. However, SOC designers can still use the MIPS kernel instruction set to meet emerging audio standards through CorExtend's features. User-defined instructions (UDI) or CorExtend add new instructions and states for application acceleration. This customization capability provides SOC vendors with the ability to improve performance and product personalization.

Migration route

MIPS Technologies continues to develop increasingly advanced core designs and achieve architectural advancements, with extensive experience in continuously improving performance. In the core area, MIPS Technologies has added an 8-segment pipeline to the product to improve clock speed performance. In terms of architecture, MIPS Technologies has improved IPC performance by adding a Release 2 Architecture.

MIPS Technologies continues to promise to improve performance and recently released the ASE MIPS processor for Multi-Threading (MT). This product has a special relationship with the audio market. MIPS MT ASE improves the performance of the entire system by populating the fixed position of the pipeline with useful work from another available thread. However, the more significant feature of MT ASE in terms of audio is that it provides a quality of service (QoS) timing mechanism.

MT ASE uses a concept of multiple Virtual Processing Elements (VPE) that can share a single pipeline. In an audio environment, two VPEs can be used: one running the OS (operating system) and the other running the audio application. MT ASE can take advantage of timing policies to ensure that processor bandwidth allocation for specific tasks is minimized. In addition, it provides quality of service features. The combination of these two features ensures real-time execution of the audio application without skipping any audio frames, while maintaining all other real-time tasks, as well as an OS in a timely manner.

The QoS feature essentially eliminates the impact of OS interrupts on the performance of audio functions. In general, interrupt services can cause considerable variability in thread execution time for "occurring" exceptions. MT ASE provides a mechanism that can delay any asynchronous exception until the OS thread (non-exempt thread) is scheduled. This increases the interrupt latency of the OS task in a limited and controlled manner while maintaining the execution of the audio task. If the execution of the interrupt handler occurs only during the time slot in which the output time slot is not allocated to exempt the real-time QoS thread, then the interrupt service has no direct impact on such real-time code execution time.

MIPS audio decoder application example

The audio decoder is typically accessed as a driver application. The role of the driver is to extract the incoming bit stream from the appropriate input device and send the decoded bit stream to the audio output device, as shown in Figure 2. It can also perform other post-processing functions, such as bass control of the decoded audio bitstream before being sent to the output device. The drive accesses the MIPS audio product through a standard interface mechanism, which is the Soft Audio Interface (SAI) of MIPS. This universal interface allows a variety of audio decoders from MIPS Technologies to easily interface with the main application.

The MIPS SAI provides interface functions and structures between the decoder and the main program, or the advanced control and operation monitoring decoder RTOS. This interface provides an opportunity to access control decoder operations and access status and error information parameters. The interface performs three basic functions: one to initialize the decoder, the second to read the frame header, and the third to actually perform the decoding process. All decoders have a pre-acknowledged field data structure associated with a particular decoder. The decoder reads and structure updates all frames. At the beginning or end of the frame, the main program can access the data structure, read the status or change the control parameters. Refer to the code example below, which shows how the driver works. The functions of MIPS SAI are indicated in bold.

Int main(void)

{

Decoder_specific_struct dec_ptr;

//Initialize the decoder.

Mips_sai_dec_init(&dec_ptr);

//Open the bitstream input device.

Open_input();

//Open the audio output device.

Open_output();

//Allocate buffers for decoder operation.

Allocate_buffers(&dec_ptr);

While(not-end-of-input-bitstream)

//Read the input bitstream.

Read_input(&dec_ptr);

//Read the frame header for encoded stream parameters.

Mips_sai_dec_readheader(&dec_ptr);

//Set up params for decoder operation.

Setup_params(&dec_ptr);

//Decode the frame

Mips_sai_dec_process(&dec_ptr);

//write the decoder output to the device driver.

Write_output(&dec_ptr);

End-while

//Close the input and output devices.

Close_input();

Close_output();

Return 0;

}

Conclusion

The various features available in the MIPS processor provide a number of advantages for implementing consumer audio algorithms. These advantages include a single programmable architecture, lower system cost, and reduced time to market. This makes the MIPS processor a viable and attractive solution for consumer electronics audio applications ranging from battery-powered mobile audio players to high-performance DVD recording devices.

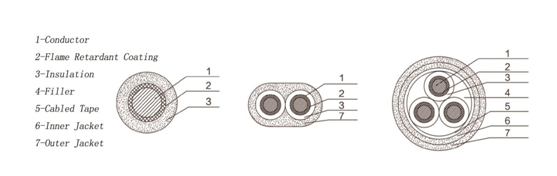

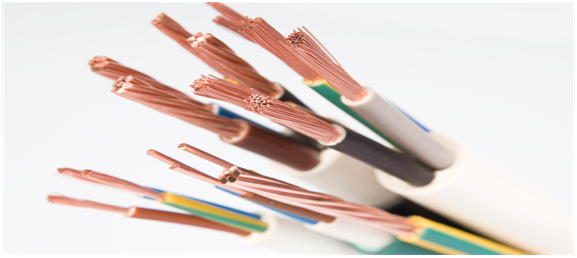

PVC Fire resistant cables(Wires) are coated with a self developed fire retardant (FR) pvc compound that halts the spread of fire even in extreme temperature cases. The compound also offers a high dielectric strength and high insulation. Fire-resistant cable can still ensure the normal operation of lines within certain time in case of combustion. It is different from the ordinary flame retardant cable in that in the event of a fire, it may continue electricity transmission. The use of this product will allow high-rise buildings, subways, power plants and other major occasions to have better fire safety and fire rescue capability.

Advantages:

- High Insulation

- Longer flex life

- Excellent electrical properties

- Chemical & acid resistance

- Large tensile strength

- Good softness

- Excellent elasticity and stickiness

Standard:

GB/T19216.21

Rated Voltage:

450/750V

Application:

This cable is designed for areas where the integrity of the electrical circuit is critical in maintaining power supply. Applications can be found in emergency lightings, control and power circuits, power stations, fire alarm systems, underground tunnels, communication systems, sewage treatment plants, lifts, escalators and high-rise buildings

Welcome to visit our factory to learn more about us. If you have any questions, please feel free to contact us.

PVC Insulated Fire Resistant Wire

PVC Insulated Fire Resistant Wire,Fire Resistant Cable,Heat Resistant Electrical Wire,Fire Resistant PVC Insulated Copper Wire

Fujian Lien Technology Co.,Ltd , http://www.liencable.com